Readings Newsletter

Become a Readings Member to make your shopping experience even easier.

Sign in or sign up for free!

You’re not far away from qualifying for FREE standard shipping within Australia

You’ve qualified for FREE standard shipping within Australia

The cart is loading…

This title is printed to order. This book may have been self-published. If so, we cannot guarantee the quality of the content. In the main most books will have gone through the editing process however some may not. We therefore suggest that you be aware of this before ordering this book. If in doubt check either the author or publisher’s details as we are unable to accept any returns unless they are faulty. Please contact us if you have any questions.

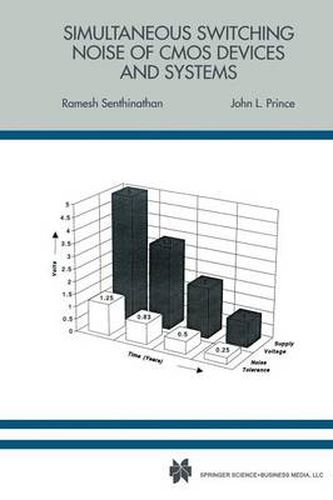

This monograph presents our recent research on Simultaneous Switching Noise (SSN) and related issues for CMOS based systems. Although some SSN related work was previously reported in the literature, it were mainly for Emitter Coupled Logic (ECL) gates using Bipolar Junction Transistors (BJTs). This present work covers in-depth analysis on estimating SSN and its impact for CMOS based devices and systems. At present semiconductor industries are moving towards scaled CMOS devices and reduced supply voltage. SSN together with coupled noise may limit the packing density, and thereby the frequency of operation of packaged systems. Our goal is to provide efficient and yet reliable methodologies and algorithms to estimate the overall noise containment in single chip and multi-chip package assemblies. We hope that the techniques and results described in this book will be useful as guides for design, package, and system engineers and academia working in this area. Through this monograph, we hope that we have shown the necessity of interactions that are essential between chip design, system design and package design engineers to design and manufacture optimal packaged systems. Work reported in this monograph was partially supported by the grant from Semiconductor Research Corporation (SRC Contract No. 92-MP-086).

$9.00 standard shipping within Australia

FREE standard shipping within Australia for orders over $100.00

Express & International shipping calculated at checkout

Stock availability can be subject to change without notice. We recommend calling the shop or contacting our online team to check availability of low stock items. Please see our Shopping Online page for more details.

This title is printed to order. This book may have been self-published. If so, we cannot guarantee the quality of the content. In the main most books will have gone through the editing process however some may not. We therefore suggest that you be aware of this before ordering this book. If in doubt check either the author or publisher’s details as we are unable to accept any returns unless they are faulty. Please contact us if you have any questions.

This monograph presents our recent research on Simultaneous Switching Noise (SSN) and related issues for CMOS based systems. Although some SSN related work was previously reported in the literature, it were mainly for Emitter Coupled Logic (ECL) gates using Bipolar Junction Transistors (BJTs). This present work covers in-depth analysis on estimating SSN and its impact for CMOS based devices and systems. At present semiconductor industries are moving towards scaled CMOS devices and reduced supply voltage. SSN together with coupled noise may limit the packing density, and thereby the frequency of operation of packaged systems. Our goal is to provide efficient and yet reliable methodologies and algorithms to estimate the overall noise containment in single chip and multi-chip package assemblies. We hope that the techniques and results described in this book will be useful as guides for design, package, and system engineers and academia working in this area. Through this monograph, we hope that we have shown the necessity of interactions that are essential between chip design, system design and package design engineers to design and manufacture optimal packaged systems. Work reported in this monograph was partially supported by the grant from Semiconductor Research Corporation (SRC Contract No. 92-MP-086).